Разрядность АЦП определяется динамическим диапазоном

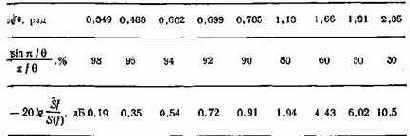

Таблица 3.9

Разрядность АЦП определяется динамическим диапазоном входного сигнала и допустимыми шумами квантования. Если на вход АЦП подается сигнал с максимальной амплитудой UMaKC и дисперсией шума ст2ш, то шаг квантования А обычно выбирается равным 1 — Зстш. При увеличении А снижается отношение сигнал/шум на выходе АЦП. Это снижение называют потерями квантования и определяют следующим образом:

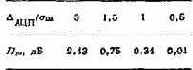

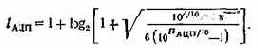

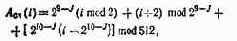

где ДАцп, б2ацп — шаг квантования и дисперсия шумов АЦП (при ААЦп<Збш, б2ацп=Д2ацп/12).

В табл. 3.9 приведены некоторые значения Пкв для различных соотношений Ддцп и стш.

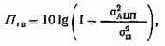

Выбрав из табл. 3.9 значения Якв, с учетом заданного значения динамического диапазона d определяется разрядность АЦП Г21:

Таким образом, можно рекомендовать следующий порядок выбора типа АЦП:

1) в соответствии с (3.14) определяется FA;

2) исходя из заданного уровня потерь Пзад и fc определяются Ф, П9, Пкв. При этом потери ПАцп = Пф+ПКв<П3ад;

3) определяется минимальное значение lацп. удовлетворяющее п. 2;

4) Из табл. 1.6 выбираются АЦП, удовлетворяющие пп. 1), 2),3).

3.6. АЛГОРИТМ КОНСТРУКТОРСКОГО СИНТЕЗА

И ОЦЕНКИ ЭФФЕКТИВНОСТИ РАЗЛИЧНЫХ ВАРИАНТОВ

РЕАЛИЗАЦИИ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

Решение задачи конструкторского синтеза и оценки эффективности различных вариантов реализации МПУ включает следующие этапы: анализ требований реализации заданного алгоритма; построение различных вариантов МПУ; оценка конкурирующих вариантов и выбор наиболее эффективного из них.

Рассмотрим алгоритм выполнения этих этапов на примере проектирования цифрового спектроанализатора, реализованной на основе алгоритма БПФ. Исходными данными являются: диапазон анализируемых частот 200 кГц; длительность сигнала 2,5 мс: динамический диапазон по входу 30 дБ; амплитуда входного сигнала 63 мВ; среднее квадратическое значение шума на входе 2 мВ; величина внеполосного затухания 40 дБ; несущая частота 20 МГц; полоса .пропускания эквивалентного фильтра не более 550 Гц; число подмассивов обработки 1.

Микропроцессорное уст ройство реализуется на печатных платах с одно- или двухсторонней компоновкой; при этом удельная мощность рассеивания не более 0,08 Вт/см2, наработка на отказ не менее 20 000 ч.

Анализ требований реализации заданного алгоритма. Задачей этого этапа является определение параметров спектроанализатора, необходимых для построения различных вариантов МПУ. Как известно [2], применяются, в основном, два варианта построения спектроанализатора: с формирователем квадратур (ФК) (см. рис. 2.5) и без него. Использование ФК позволяет в 2 раза снизить .Рд при параллельной работе двух АЦП в каналах ФК. Недостатком такой структуры является ограниченный динамический диапазон входного сигнала. Из табл. 3.1 и 3.2 определяем, что для обеспечения уровня ложных сигналов не выше 40 дБ нелинейность амплитудных характеристик должна быть не более 1%, а отклонение разности фаз в квадратурных каналах от п/2 не более 1°. Для обеспечения такой точности необходимо в алгоритм спектрального анализа ввести коррекцию мнимой и действительной частей входных отсчетов. При дискретизации на несущей частоте вдвое увеличивается входной массив, что потребует введения дополнительного этапа вычисления! ДПФ. Поэтому, с точки зрения временных затрат, эти структурные варианты примерно равноценны.

Несущая частота равна 20 МГц. Из табл. 3.8 определяем, что для обеспечения снижения отношения сигнал-шум не более 2 — 3 дБ длительность выборки сигнала 9=0,36 Tп=9 нc. Разработка УВХ с такими параметрами представляет собой сложную задачу, поэтому выбираем структуру с ФК. Частота дискретизации входного сигнала Рд>ДF=200 кГц. Полоса пропускания эквивалентного фильтра Дf'=1/Tс=400 Гц. Число спектральных отсчетов Nc — =Тс/Тя = 500. Исходя из заданного динамического диапазона входного сигнала при условии Дацп/бш=1 определим разрядность АЦП: lАцп=] Iog2d [=5.

Для обеспечения внеполосного подавления от — 40 дБ используем весовую обработку входных отсчетов [30].

Известно, что весовая обработка приводит к расширению Дf'. Допустимое значение коэффициента расширения k<Дf/Дf'= = 1,37. Этим требованиям удовлетворяет окно Хэмминга, обеспечивающее подавление боковых лепестков до — 43 дБ и ширину полосы пропускания Дf= = 400-1,35=544 Гц.

Операция весовой обработки (как и операция коррекции) сводится к умножению входных отсчетов на постоянную величину. Для сокращения аппаратурных затрат целесообразно совместить выполнение этих операций и использовать один умножитель. При этом корректирующая функция Ф должна учитывать значения весового окна, а также параметры нелинейности и отклонения фаз квадратурных каналов.

Аппаратурные затраты МПУ и особенно ЗУ во многом определяются выбранной системой счисления. При построении цифровых устройств обработки огналов применяются системы счисления с фиксированной, плавающей и по-Слочно-плавающей запятой [30]. Методика расчета разрядности представления комплексных входных отсчетов в различных системах счисления рассмотрена в [2,30]. В этих работах показано, что в системе счисления с фиксированной Запятой разрядность комплексных отсчетов lк.ч>2(lАЦП+L), где L — число тапов вычисления БПФ. В системе счисления с плавающей запятой разрядность кодов мантиссы и порядка выбирается согласно следующим неравенствам: lк.м>lАЦП, lп=log2L. Признак переполнения отсутствует при выполнении условия: (2lАЦП — 1)>3бс(j) + 2iUвх/ДАцп , где бс (j) — суммарное сред-нее квадратическое отклонение шума, полученное в результате выполнения j-го этапа БПФ. Если данное условие не выполняется, то результат БО должен масштабироваться.

Система счисления с поблочно-плавающей запятой представляет собой комбинацию представления чисел с фиксированной и плавающей запятой. Вместо нормирования каждого представляемого числа в отдельности в данной системе один и тот же порядок используется для представления целого массива (блока) чисел. Для этого из массива выбирается наибольшее число и представляется с плавающей запятой для определения общего порядка.

Значения остальных (меньших) чисел содержат их мантиссы. С точки зрения ис пользуемой емкости памяти система счисления с поблочно-плавающей запятой более экономична. С учетом методики, изложенной в [2], найдем разрядность представления чисел в различных системах счисления: с фиксированной запятой lк.ч>30, с плавающей lк.ч>22, с поблочно-плавающей lк.ч>18. С точки зрения экономики памяти целесообразно выбрать систему счисления с поблочно-плавающей запятой. Однако поскольку массив обрабатываемых отсчетов невелик, оценим объем сэкономленной памяти:

ДEОЗУ = 2NХДl=1КХ14.

Достигнутый аппаратурный выигрыш составляет две микросхемы емкостью 2КХ8. Вместе с тем использование системы счисления с поблочно-плавающей запятой требует введения дополнительных операций масштабирования, что усложняет структуру МП БО. Поэтому в данном случае выбираем систему счисления с фиксированной запятой.

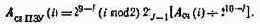

Алгоритм спектрального анализа приведен на рис. 3.12,а. На вход устройства поступают отсчеты с Гд=5 мкс. Блок коррекции выполняет умножение входных отсчетов на значения корректирующей функции, которые хранятся в ППЗУ, емкостью NX 16. В регистрах Pcl — Ргб записаны основные параметры обрабатываемого массива: начальный адрес массива входных отсчетов {Pel), начальный адрес массива поворачивающих коэффициентов (Рг2), число БО, выполняемых на каждом этапе вычислений (РгЗ), текущий номер выполняемого этапа БПФ или номер итерации (Рг4), число итераций, необходимых для выполнения БПФ (Рг5) и текущей номер выполняемой БО (Ргб).

Вычисление текущих значений адресов входных отсчетов осуществляется с учетом необходимости перестановки данных после выполнения каждого этапа БПФ [30]. После выполнения 256 БО изменяется текущее значение номера итерации, что учитывается при вычислении значений адресов. После вычисления L итераций в ОЗУ записаны 512 комплексных значений спектральных-отсчетов входного сигнала.

В качестве базиса описания алгоритма, изображенного на рис. 3.12,а, примем команды, приведенные в табл. 3.5 и дополненные подпрограммами коррекции входных отсчетов, выполнения БО и вычисления текущего значения адресов.

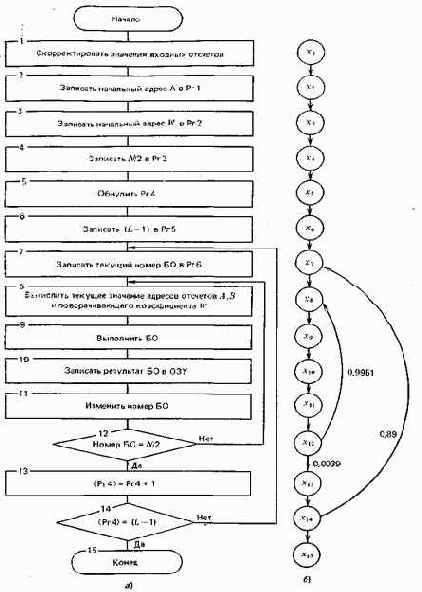

На каждой итерации вычисления БПФ выполняется N/2 БО, в которык участвует N отсчетов, разбитых на N/2J групп, где J — номер выполняемом итерации. Считаем, что в данном случае применяется алгоритм БПФ с замещением, т. е. результаты выполнения БО записываются в те же ячейки ОЗУ, ив которых считывались исходные данные. В этом случае алгоритм формирования адресов считывания ОЗУ при коэффициенте распараллеливания Kр = 1 может быть представлен следующим выражением [2]: 1

где t=0, 1..... (NL — 1) — номер формируемого адреса.

Реализация этого алгоритма может быть осуществлена двоичным счетчиком, первый разряд которого выполняет функцию i mod 2. Умножение этого разряда на 29-J увеличивает вес разряда в формируемом адресе. Как следует из алгоритма, на первой итерации этот вес равен 8, на второй 7 и т. д. Второе слагаемое алгоритма определяет вес разрядов счетчика, начиная со второго. На первой итерации разрядам 2 — 9 счетчика присваиваются веса с первого по восьмой, на второй итерации — с первого по седьмой и т. д. На девятой итерации значение (i-2)mod 1 равно 0. Третье слагаемое уравнения (3.17) реализуется использованием соответствующих разрядов счетчика. На первой итерации значение 210((4-210)mod 512 равно 0. На второй итерации девятый разряд счетчика является девятым разрядом адреса считывания. На третьей итерации девятый и восьмой разряды являются девятым и восьмым разрядом АСч. На девятой итерации разряды счетчика со второго по девятый соответствуют аналогичным разрядам АСч-

Адреса считывания поворачивающих коэффициентов W формируются следующим образом:

Алгоритмы (3.17) и (3.18) могут быть реализованы программно и аппа-ратно. Так как системы команд МП, приведенных в табл. 1.2, не ориентированы на выполнение операций с отдельными битами, то программная реализация алгоритма (3.17) потребует не менее 10 микрокоманд.

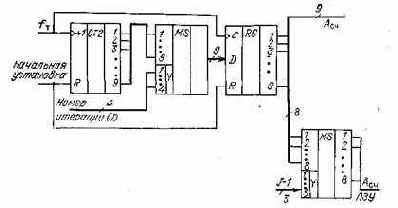

Один из вариантов аппаратной реализации алгоритма формирования адресов считывания приведен на рис. 3.13 [2]. Разряды 9-разрядного счетчика реализуют отдельные слагаемые алгоритма (3.17) в соответствии с приведенным выше описанием. Коммутация разрядов счетчика (изменение их веса) осуществляется мультиплексорами, управление которыми производится кодом номера итерации. При реализации устройства на микросхемах серии 133 необходимы 3 микросхемы 133ИЕ7, 17 микросхем 133КП5 и 2 микросхемы 133ИР13. Время формирования адреса одного отсчета около 300 не.

Небольшой объем обрабатываемого массива данных позволяет реализовать формирователь адресов считывания ОЗУ и ПЗУ на микросхемах памяти. Чио ло адресов ОЗУ JVL=4608, ПЗУ=256-8=2048. Разрядность адреса считывания ОЗУ A'CЧ = ]log2NL[=13; A'счпзу = 11. Устройство формирования адресов может быть реализовано на трех микросхемах РПЗУ с ультрафиолетовым стиранием информации К573РФ6 емкостью 8К.Х8 либо на других микросхемах (см. табл. 1.5).

Коррекция входных отсчетов заключается в умножении этих отсчетов, поступающих с АЦП, на значения корректирующей функции, хранимые в ППЗУ емкостью 512 слов. Особенностью данного алгоритма является ограниченный динамический диапазон входного сигнала, а следовательно, и небольшая разрядность входных отсчетов (6 бит). Это позволяет реализовать коррекцию входных отсчетов на ПЗУ, выполняющем роль умножителя. На адресные входы ПЗУ подаются два числа: множитель и множимое. В ячейке ПЗУ, адрес которой равен коду перемножаемых чисел, хранится их произведение. Поскольку разрядность входных отсчетов 6 бит, разрядность корректирующей функции тоже может быть принята 6 бит. Для реализации такого умножителя необходимо взять БИС ПЗУ, имеющую не менее 4К адресуемых ячеек.

Рис. 3.12. Структурная схема алгоритма спектрального анализа (а) и его графовая модель (б)